### 600 MHz Dual Integrated DCL with PPMU, VHH Drive Capability, Level Setting DACs, and On-Chip Calibration Engine

# ADATE318

#### **FEATURES**

600 MHz/1200 Mbps data rate 3-level driver with high-Z and reflection clamps Window and differential comparators ±25 mA active load Per pin PPMU with -2.0 V to +6.5 V range Low leakage mode (typically 4 nA) Integrated 16-bit DACs with offset and gain correction High speed operating voltage range: -1.5 V to +6.5 V Dedicated VHH output pin range: 0.0 V to 13.5 V 1.1 W power dissipation per channel Driver 3-level voltage range: -1.5 V to +6.5 V Precision trimmed output resistance Unterminated swing: 200 mV minimum to 8 V maximum 725 ps minimum pulse width, VIH – VIL = 2.0 V Comparator Differential and single-ended window modes >1.2 GHz input equivalent bandwidth Load ±25 mA current range Per pin PPMU (PPMU) Force voltage/compliance range: -2.0 V to +6.5 V 5 current ranges: 40 mA, 1 mA, 100 µA, 10 µA, 2 µA **External sense input for system PMU** Go/no-go comparators Levels Fully integrated 16-bit DACs On-chip gain and offset calibration registers and add/multiply engine Package 84-lead 10 mm × 10 mm LFCSP (0.4 mm pitch) **APPLICATIONS** Automatic test equipment Semiconductor test systems

#### **GENERAL DESCRIPTION**

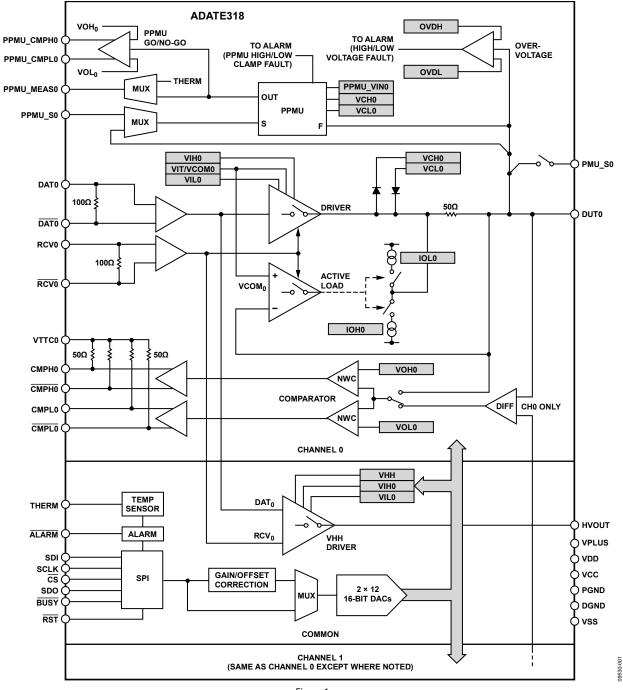

The ADATE318 is a complete, single-chip ATE solution that performs the pin electronics functions of driver, comparator, and active load (DCL), four quadrant, per pin, parametric measurement unit (PPMU). It has VHH drive capability per chip to support flash memory testing applications and integrated 16-bit DACs with an on-chip calibration engine to provide all necessary dc levels for operation of the part.

The driver features three active states: data high, data low, and terminate mode, as well as a high impedance inhibit state. The inhibit state, in conjunction with the integrated dynamic clamps, facilitates the implementation of a high speed active termination. The output voltage capability is -1.5 V to +6.5 V to accommodate a wide range of ATE and instrumentation applications.

The ADATE318 can be used as a dual, single-ended drive/ receive channel or as a single differential drive/receive channel. Each channel of the ADATE318 features a high speed window comparator as well as a programmable threshold differential comparator for differential ATE applications. A four quadrant PPMU is also provided per channel.

All dc levels for DCL and PPMU functions are generated by 24 on-chip 16-bit DACs. To facilitate accurate levels programming, the ADATE318 contains an integrated calibration function to correct gain and offset errors for each functional block. Correction coefficients can be stored on chip, and any values written to the DACs are automatically adjusted using the appropriate correction factors.

The ADATE318 uses a serial programmable interface (SPI) bus to program all functional blocks, DACs, and on-chip calibration constants. It also has an on-chip temperature sensor and over/undervoltage fault clamps for monitoring and reporting the device temperature and any output pin or PPMU voltage faults that may occur during operation.

#### Rev. A

**Board test systems**

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

Instrumentation and characterization equipment

### TABLE OF CONTENTS

| Features                                           |

|----------------------------------------------------|

| Applications1                                      |

| General Description 1                              |

| Revision History 2                                 |

| Functional Block Diagram 3                         |

| Specifications                                     |

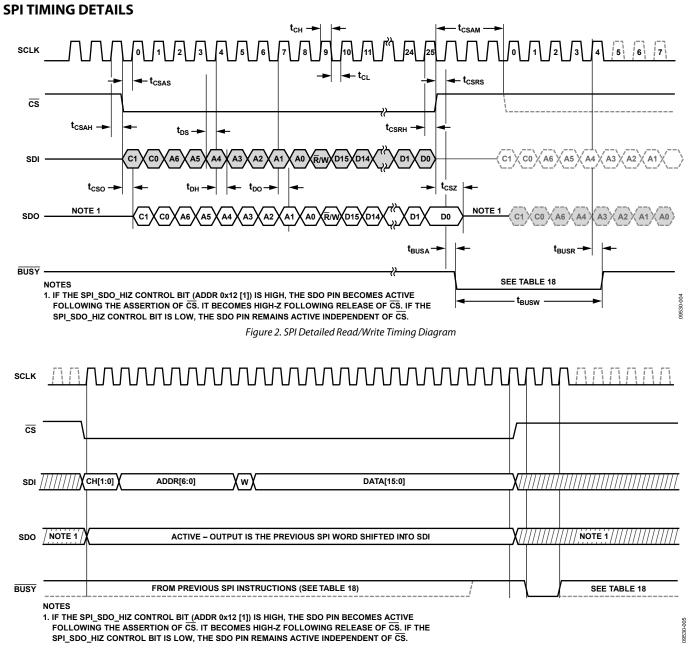

| SPI Timing Details                                 |

| Absolute Maximum Ratings27                         |

| Thermal Resistance                                 |

| ESD Caution27                                      |

| Pin Configuration and Function Descriptions        |

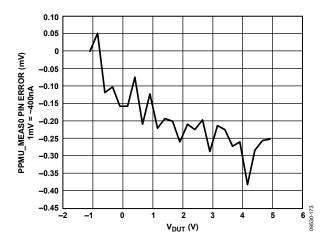

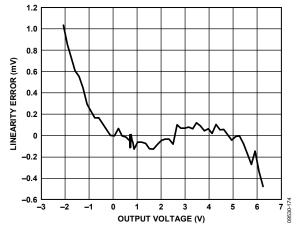

| Typical Performance Characteristics                |

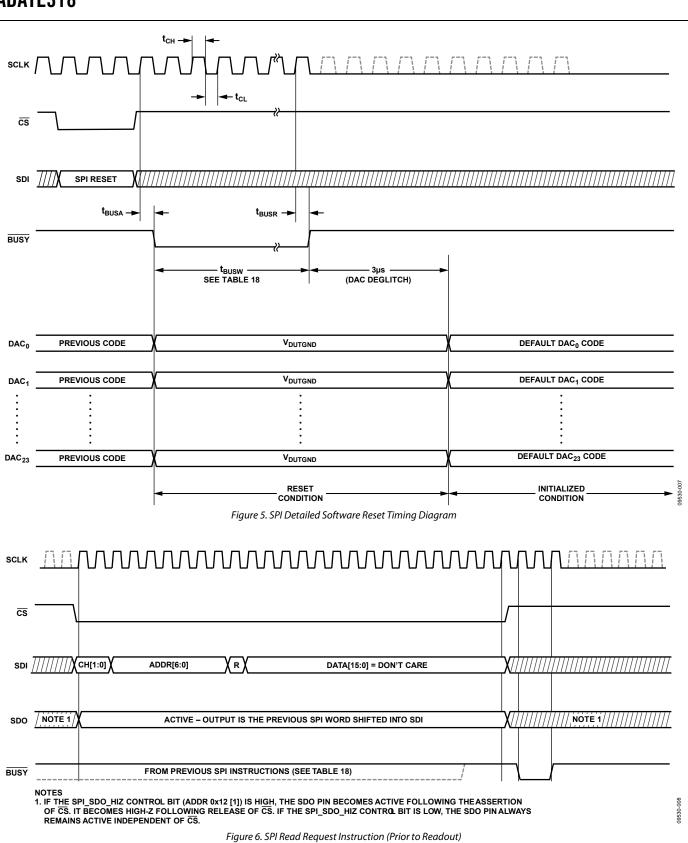

| SPI Interconnect Details                           |

| Use of the SPI BUSY Pin                            |

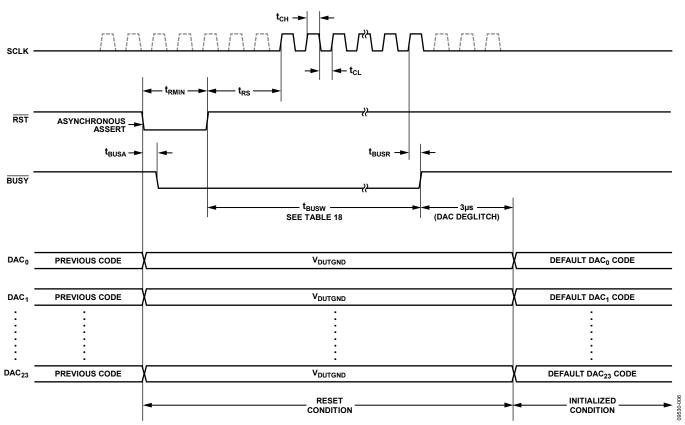

| Reset Sequence and the $\overline{\text{RST}}$ Pin |

| SPI Register Definitions and Memory Map52          |

| Control Register Details55                         |

### **REVISION HISTORY**

| 7/11—Rev. 0 to Rev. A            |    |

|----------------------------------|----|

| Updated Outline Dimensions       | 80 |

| 4/11—Revision 0: Initial Version |    |

#### FUNCTIONAL BLOCK DIAGRAM

Figure 1.

### **SPECIFICATIONS**

Positive Supply Current, VDD

Negative Supply Current, VSS

**Total Power Dissipation**

VDD = +10.0 V, VCC = +2.5 V, VSS = -6.0 V, VPLUS = +16.75 V, VTTCx = +1.2 V, VREF = 5.000 V, VREFGND = 0.000 V. All test conditions are as defined in Table 32. All specified values are at  $T_1 = 50^{\circ}C$ , where  $T_1$  corresponds to the internal temperature sensor reading (THERM pin), unless otherwise noted. Temperature coefficients are measured around  $T_1 = 50^{\circ} \pm 20^{\circ}C$ , unless otherwise noted. Typical values are based on statistical mean of design, simulation analyses, and/or limited bench evaluation data. Typical values are neither tested nor guaranteed. See Table 16 for an explanation of test levels.

#### Test Parameter Min Тур Max Unit l evel Conditions TOTAL FUNCTION Output Leakage Current, DCL Disable **PPMU** Range E -10.0 ±4.0 +10.0 nA Ρ -2.0 V < VDUTx < +6.5 V, PPMU and DCL disabled, PPMU Range E, VCL = -2.5 V, VCH = +7.5 V PPMU Range A, Range B, Range C, and ±4.0 nA Ст -2.0 V < VDUTx < +6.5 V, PPMU and DCL disabled, PPMU Range D Range A, Range B, Range C, Range D, VCL = -2.5 V, VCH = +7.5 V -2.0 V < VDUTx < +7.0 V, PPMU disabled and DCL enabled, Output Leakage Current, -2 +2 μΑ Ρ Driver High-Z Mode RCVx active, VCL = -2.5 V, VCH = +7.5 V S Drive VIT = 0.0 V DUTx Pin Capacitance 1.2 рF D DUTx Pin Voltage Range -2.0 +7.0 V POWER SUPPLIES Total Supply Range, 22.75 23.55 V D VPLUS to VSS VPLUS Supply, VPLUS 15.90 16.75 17.60 ٧ D Defines dc PSR conditions Defines dc PSR conditions 9.5 10.0 10.5 D Positive Supply, VDD v Negative Supply, VSS -6.3 -6.0 -5.7 v D Defines dc PSR conditions Logic Supply, VCC 2.3 2.5 3.5 ٧ D Defines dc PSR conditions D Comparator Output Termination, VTTCx 05 12 3.3 V Ρ VPLUS Supply Current, VPLUS 1.1 2.5 mA VHH pin disabled 4.75 13.28 16.25 Ρ VHH pin enabled, RCVx active, no load, mA VHH programmed level = 13.0 V Р -125 +125 Quiescent (SPI is static); VCC = 2.5 V Logic Supply Current, VCC 1 μA 7.5 mΑ S Current drawn during clocked portion of device reset sequence 45 50 Ρ Termination Supply Current, VTTCx 30 mA Positive Supply Current, VDD 90 99 115 mΑ Ρ Load power-down (IOH = IOL = 0 mA) Negative Supply Current, VSS 155 172 185 mΑ Р Load power-down (IOH = IOL = 0 mA) Ρ w **Total Power Dissipation** 1.9 2.1 2.3 Load power-down (IOH = IOL = 0 mA) Positive Supply Current, VDD 145 174 210 mΑ Ρ Load active off (IOH = IOL = 25 mA)Ρ Load active off (IOH = IOL = 25 mA)Negative Supply Current, VSS 210 246 280 mΑ W Ρ Load active off (IOH = IOL = 25 mA)**Total Power Dissipation** 3.0 3.3 3.6 Ст Positive Supply Current, VDD 167 Load active off (IOH = IOL = 25 mA), calibrated mA Negative Supply Current, VSS 238 mΑ CT Load active off (IOH = IOL = 25 mA), calibrated **Total Power Dissipation** 3.2 W Ст Load active off (IOH = IOL = 25 mA), calibrated

#### **Table 1. Detailed Electrical Specifications**

mA

mΑ

W

Ст

Ст

Ст

Load power-down, PPMU standby

Load power-down, PPMU standby

Load power-down, PPMU standby

109

183

2.3

| Parameter                                             | Min   | Тур   | Max   | Unit | Test<br>Level | Conditions                                                                                                    |

|-------------------------------------------------------|-------|-------|-------|------|---------------|---------------------------------------------------------------------------------------------------------------|

| TEMPERATURE MONITOR                                   |       |       |       |      |               |                                                                                                               |

| Temperature Sensor Gain                               |       | 10    |       | mV/K | D             |                                                                                                               |

| Temperature Sensor Accuracy over<br>Temperature Range |       | ±6    |       | К    | C⊤            |                                                                                                               |

| VREF INPUT REFERENCE                                  |       |       |       |      |               |                                                                                                               |

| DAC Reference Input Voltage Range<br>(VREF Pin)       | 4.950 | 5.000 | 5.050 | V    | D             | Provided externally:<br>VREF pin = +5.000 V<br>VREFGND pin = 0.000 V (not referenced to V <sub>DUTGND</sub> ) |

| Input Bias Current                                    |       |       | 100   | μΑ   | Р             | Tested with 5.000 V applied                                                                                   |

| DUTGND INPUT                                          |       |       |       |      |               |                                                                                                               |

| Input Voltage Range,<br>Referenced to AGND            | -0.1  |       | +0.1  | V    | D             |                                                                                                               |

| Input Bias Current                                    | -100  |       | +100  | μΑ   | Р             | Tested at –100 mV and +100 mV                                                                                 |

### Table 2. Driver (VIH – VIL $\ge$ 100 mV to Meet DC and AC Performance Specifications)

| <u> </u>                                               |      |      |      |        | Test  |                                                                                                                                                                                               |

|--------------------------------------------------------|------|------|------|--------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Parameter                                              | Min  | Тур  | Max  | Unit   | Level | Conditions                                                                                                                                                                                    |

| DC SPECIFICATIONS                                      |      |      |      |        |       |                                                                                                                                                                                               |

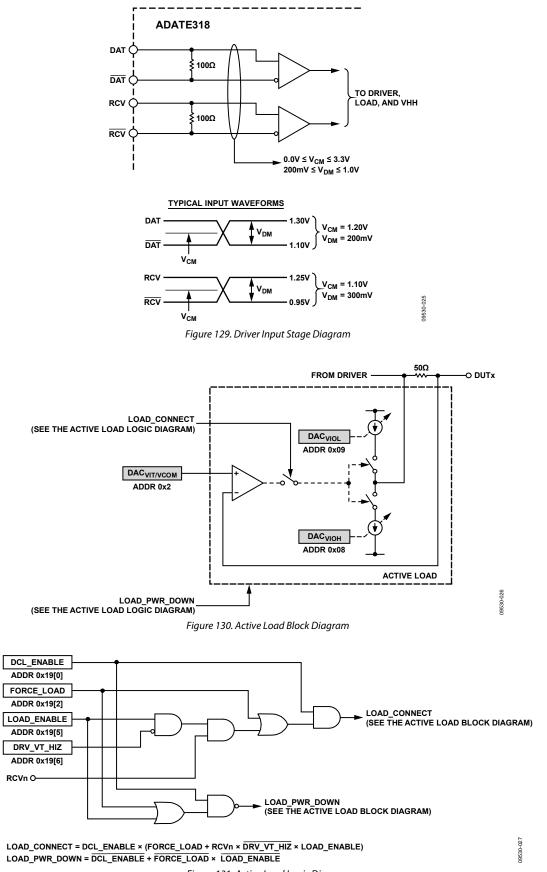

| High-Speed Differential Input<br>Characteristics       |      |      |      |        |       |                                                                                                                                                                                               |

| High Speed Input Termination<br>Resistance: DATx, RCVx | 92   | 100  | 108  | Ω      | Р     | Impedance between each pair of DATx and RCVx pins;<br>push 4 mA into positive pin, force 0.8 V on negative pin,<br>measure voltage between pins; calculate resistance ( $\Delta V/\Delta I$ ) |

| Input Voltage Differential: DATx, RCVx                 | 0.2  | 0.4  | 1.0  | V      | D     | $0.2 V < V_{DM} < 1.0 V$                                                                                                                                                                      |

| Input Voltage Range: DATx, RCVx                        | 0.0  |      | 3.3  | V      | D     | $0.0 \text{ V} < (V_{CM} \pm V_{DM}/2) < 3.3 \text{ V}$                                                                                                                                       |

| Output Characteristics                                 |      |      |      |        |       |                                                                                                                                                                                               |

| Output High Range, VIH                                 | -1.4 |      | +6.5 | V      | D     |                                                                                                                                                                                               |

| Output Low Range, VIL                                  | -1.5 |      | +6.4 | V      | D     |                                                                                                                                                                                               |

| Output Term Range, VIT                                 | -1.5 |      | +6.5 | V      | D     |                                                                                                                                                                                               |

| Functional Amplitude<br>(VIH – VIL)                    | 0.0  | 8.0  |      | V      | D     |                                                                                                                                                                                               |

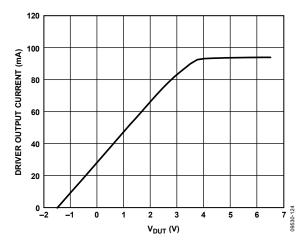

| DC Output Current Limit Source                         | 75   |      | 130  | mA     | Р     | Drive high, VIH = $+6.5$ V, short DUTx pin to $-1.5$ V, measure current                                                                                                                       |

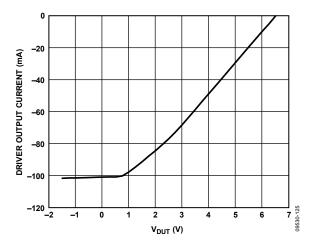

| DC Output Current Limit Sink                           | -130 |      | -75  | mA     | Р     | Drive low, VIL = $-1.5$ V, short DUTx pin to $+6.5$ V, measure current                                                                                                                        |

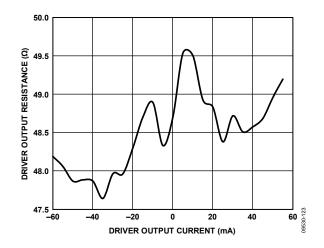

| Output Resistance, ±40 mA                              | 46   | 48.6 | 51   | Ω      | Р     | $\Delta$ VDUT/ $\Delta$ IDUT; source: VIH = 3.0 V, IDUT = +1 mA, +40 mA;<br>sink: VIL = 0.0 V, IDUT = -1 mA, -40 mA                                                                           |

| DC ACCURACY                                            |      |      |      |        |       | VIH tests with VIL = $-2.5$ V, VIT = $-2.5$ V<br>VIL tests with VIH = $+7.5$ V, VIT = $+7.5$ V<br>VIT tests with VIL = $-2.5$ V, VIH = $+7.5$ V, unless otherwise<br>specified                |

| VIH, VIL, VIT Offset Error                             | -500 |      | +500 | mV     | Р     | Measured at DAC Code 0x4000 (0 V), uncalibrated                                                                                                                                               |

| VIH, VIL, VIT Offset Tempco                            |      | ±625 |      | μV/°C  | CT    |                                                                                                                                                                                               |

| VIH, VIL, VIT Gain                                     | 1.0  |      | 1.1  | V/V    | Ρ     | Gain derived from measurements at DAC Code 0x4000<br>(0 V) and DAC Code 0xC000 (5 V); based on ideal DAC<br>transfer functions (see Table 21)                                                 |

| VIH, VIL, VIT Gain Tempco                              |      | ±40  |      | ppm/°C | CT    |                                                                                                                                                                                               |

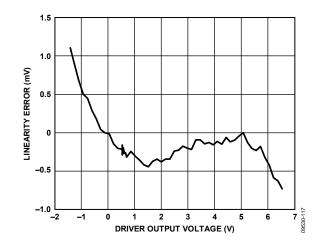

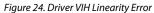

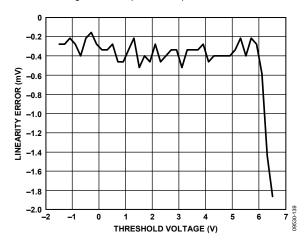

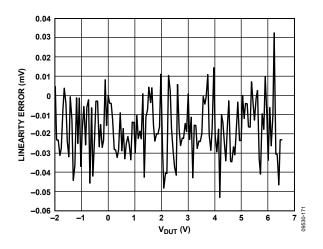

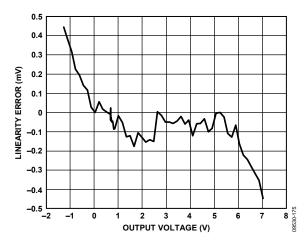

| VIH, VIL, VIT DNL                                      |      | ±1   |      | mV     | CT    | After two point gain/offset calibration; calibration points at 0x4000 (0 V) output; 0xC000 (+5 V) output; measured over full specified output range                                           |

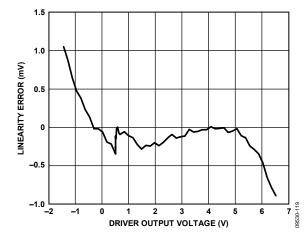

| VIH, VIL, VIT INL                                      | -7   |      | +7   | mV     | Р     | After two point gain/offset calibration; applies to nominal VDD = +10.0 V supply case only                                                                                                    |

| Parameter                                 | Min | Тур  | Max | Unit | Test<br>Level  | Conditions                                                                                                              |

|-------------------------------------------|-----|------|-----|------|----------------|-------------------------------------------------------------------------------------------------------------------------|

| VIH, VIL, VIT Resolution                  |     | 153  |     | μV   | D              |                                                                                                                         |

| DUTGND Voltage Accuracy                   | -7  | ±2   | +7  | mV   | Р              | Over $\pm 0.1$ V range; measured at end points of VIH, VIL, and VIT functional range                                    |

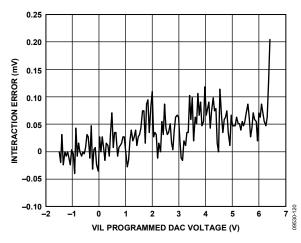

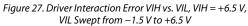

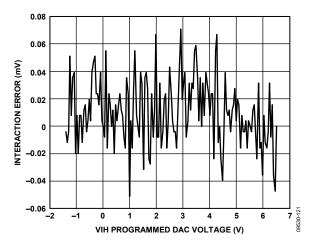

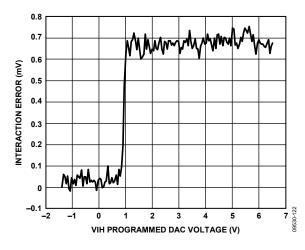

| DC Levels Interaction                     |     |      |     |      |                | DC interaction on VIL, VIH, and VIT output level while other driver DAC levels are varied                               |

| VIH vs. VIL                               |     | ±0.2 |     | mV   | CT             | Monitor interaction on VIH = +6.5 V; sweep VIL = $-1.5$ V to +6.4 V, VIT = +1.0 V                                       |

| VIH vs. VIT                               |     | ±1   |     | mV   | CT             | Monitor interaction on VIH = +6.5 V; sweep VIT = $-1.5$ V to +6.5 V, VIL = 0.0 V                                        |

| VIL vs. VIH                               |     | ±0.2 |     | mV   | CT             | Monitor interaction on VIL = $-1.5$ V; sweep VIH = $-1.4$ V to $+6.5$ V, VIT = $+1.0$ V                                 |

| VIL vs. VIT                               |     | ±1   |     | mV   | CT             | Monitor interaction on VIL = $-1.5$ V; sweep VIT = $-1.5$ V to $+6.5$ V, VIH = $+2.0$ V                                 |

| VIT vs. VIH                               |     | ±1   |     | mV   | CT             | Monitor interaction on VIT = +1.0 V; sweep VIH = $-1.4$ V to +6.5 V, VIL = $-1.5$ V                                     |

| VIT vs. VIL                               |     | ±1   |     | mV   | CT             | Monitor interaction on VIT = +1.0 V; sweep VIL = -1.5 V to +6.4 V, VIH = +6.5 V                                         |

| Overall Voltage Accuracy                  |     | ±8   |     | mV   | CT             | VIH – VIL $\ge$ 100 mV; sum of INL, dc interaction, DUTGND, and tempco errors over $\pm 5^{\circ}$ C, after calibration |

| VIH, VIL, VIT DC PSRR                     |     | ±10  |     | mV/V | C⊤             | Measured at calibration points                                                                                          |

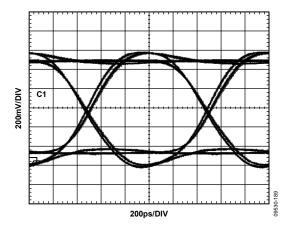

| AC SPECIFICATIONS                         |     |      |     |      |                | All ac specifications performed after calibration                                                                       |

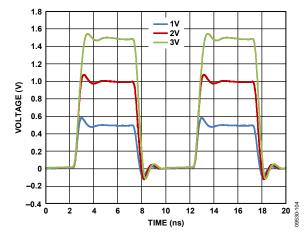

| Rise/Fall Times                           |     |      |     |      |                | Toggle DATx                                                                                                             |

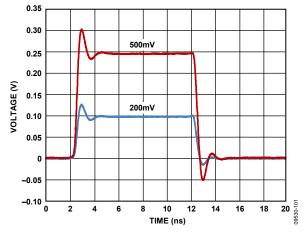

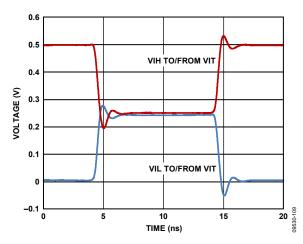

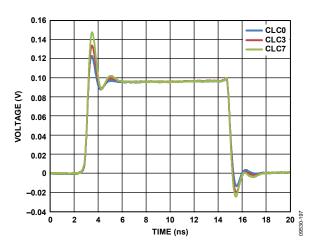

| 0.2 V Programmed Swing, T <sub>RISE</sub> |     | 215  |     | ps   | CB             | 20% to 80%, VIH = 0.2 V, VIL = 0.0 V, terminated                                                                        |

| 0.2 V Programmed Swing, TFALL             |     | 277  |     | ps   | CB             | 20% to 80%, VIH = 0.2 V, VIL = 0.0 V, terminated                                                                        |

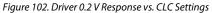

| 0.5 V Programmed Swing, T <sub>RISE</sub> |     | 218  |     | ps   | CB             | 20% to 80%, VIH = 0.5 V, VIL = 0.0 V, terminated                                                                        |

| 0.5 V Programmed Swing, TFALL             |     | 274  |     | ps   | CB             | 20% to 80%, VIH = 0.5 V, VIL = 0.0 V, terminated                                                                        |

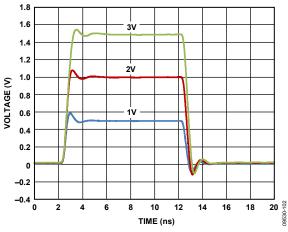

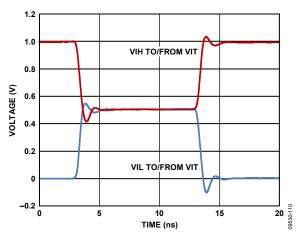

| 1.0 V Programmed Swing, $T_{RISE}$        | 150 | 222  | 320 | ps   | Р              | 20% to 80%, VIH = 1.0 V, VIL = 0.0 V, terminated                                                                        |

| 1.0 V Programmed Swing, $T_{FALL}$        | 150 | 283  | 320 | ps   | Р              | 20% to 80%, VIH = 1.0 V, VIL = 0.0 V, terminated                                                                        |

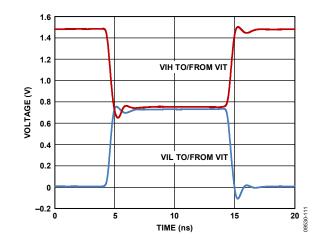

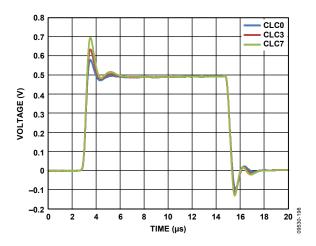

| 2.0 V Programmed Swing, $T_{RISE}$        |     | 297  |     | ps   | CB             | 20% to 80%, VIH = 2.0 V, VIL = 0.0 V, terminated                                                                        |

| 2.0 V Programmed Swing, TFALL             |     | 322  |     | ps   | CB             | 20% to 80%, VIH = 2.0 V, VIL = 0.0 V, terminated                                                                        |

| $3.0 V Programmed Swing, T_{RISE}$        |     | 447  |     | ps   | CB             | 20% to 80%, VIH = 3.0 V, VIL = 0.0 V, terminated                                                                        |

| 3.0 V Programmed Swing, $T_{FALL}$        |     | 397  |     | ps   | CB             | 20% to 80%, VIH = 3.0 V, VIL = 0.0 V, terminated                                                                        |

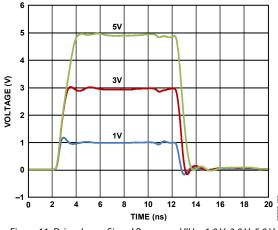

| 5.0 V Programmed Swing, $T_{RISE}$        |     | 1117 |     | ps   | C <sub>B</sub> | 10% to 90%, VIH = 5.0 V, VIL = 0.0 V, unterminated                                                                      |

| 5.0 V Programmed Swing, TFALL             |     | 798  |     | ps   | CB             | 10% to 90%, VIH = 5.0 V, VIL = 0.0 V, unterminated                                                                      |

| Rise to Fall Matching                     |     | -25  |     | ps   | Св             | Rise to fall within one channel, $VIH = 2.0 V$ , $VIL = 0.0 V$ , terminated                                             |

|                                           |     | -61  |     | ps   | C <sub>B</sub> | Rise to fall within one channel; $VIH = 1.0 V$ , $VIL = 0.0 V$ , terminated                                             |

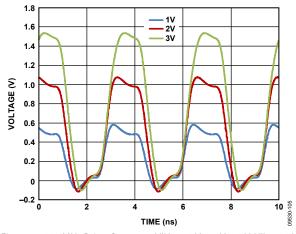

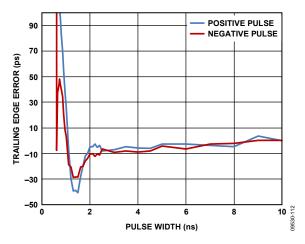

| Minimum Pulse Width                       |     |      |     |      |                | Toggle DATx                                                                                                             |

| 0.5 V Programmed Swing                    |     | 725  |     | ps   | CB             | VIH = 0.5 V, VIL = 0.0 V, terminated, timing error less than $+69/-33$ ps                                               |

|                                           |     | 725  |     | ps   | C <sub>B</sub> | VIH = 0.5 V, $VIL = 0.0 V$ , terminated, less than 10% amplitude loss                                                   |

| Maximum Toggle Rate                       |     | 2040 |     | Mbps | C <sub>B</sub> | VIH = 0.5 V, $VIL$ = 0.0 V, terminated, less than 10% loss at 50% duty                                                  |

| 1.0 V Programmed Swing                    |     | 725  |     | ps   | Св             | VIH = 1.0 V, VIL = 0.0 V, terminated, timing error less than $+58/-35$ ps                                               |

|                                           |     | 725  |     | ps   | Св             | VIH = 1.0 V, $VIL = 0.0 V$ , terminated, less than 10% amplitude loss                                                   |

| Parameter                                                    | Min | Тур  | Max | Unit         | Test<br>Level  | Conditions                                                                                             |

|--------------------------------------------------------------|-----|------|-----|--------------|----------------|--------------------------------------------------------------------------------------------------------|

| Maximum Toggle Rate                                          |     | 2040 |     | Mbps         | CB             | VIH = 1.0 V, VIL = 0.0 V, terminated, less than 10% loss at 50% duty                                   |

| 2.0 V Programmed Swing                                       |     | 725  |     | ps           | Св             | VIH = 2.0 V, VIL = 0.0 V, terminated, timing error less than $+80/-48$ ps                              |

|                                                              |     | 725  |     | ps           | Св             | VIH = 2.0 V, VIL = 0.0 V, terminated, less than 10% amplitude loss                                     |

| Maximum Toggle Rate                                          |     | 1400 |     | Mbps         | C <sub>B</sub> | VIH = 2.0 V, $VIL$ = 0.0 V, terminated, less than 10% loss at 50% duty                                 |

| 3.0 V Programmed Swing                                       |     | 900  |     | ps           | Св             | VIH = 3.0 V, VIL = 0.0 V, terminated, timing error less than $+50/-83$ ps                              |

|                                                              |     | 900  |     | ps           | C <sub>B</sub> | VIH = 3.0 V, $VIL = 0.0 V$ , terminated, less than 10% amplitude loss                                  |

| Maximum Toggle Rate                                          |     | 1100 |     | Mbps         | C <sub>B</sub> | VIH = 3.0 V, VIL = 0.0 V, terminated, less than 10% amplitude loss at 50% duty cycle                   |

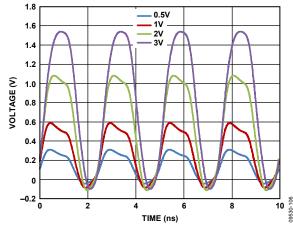

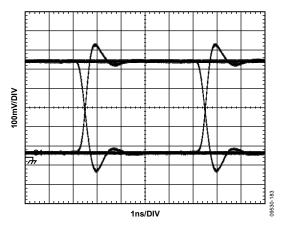

| Dynamic Performance,<br>Drive (VIH to VIL)                   |     |      |     |              |                | Toggle DATx                                                                                            |

| Propagation Delay Time                                       |     | 1.26 |     | ns           | CB             | VIH = 2.0 V, VIL = 0.0 V, terminated                                                                   |

| Propagation Delay Tempco                                     |     | 1.4  |     | ps/°C        | CB             | VIH = 2.0 V, VIL = 0.0 V, terminated                                                                   |

| Delay Matching, Edge to Edge                                 |     | 43   |     | ps           | C <sub>B</sub> | VIH = 2.0 V, VIL = 0.0 V, terminated, rising vs. falling                                               |

| Delay Matching, Channel to Channel                           |     | 32   |     | ps           | C <sub>B</sub> | VIH = 2.0 V, VIL = 0.0 V, terminated, rising vs. rising, falling vs. falling                           |

| Delay Change vs. Duty Cycle                                  |     | -28  |     | ps           | CB             | $VIH=2.0\ V,\ VIL=0.0\ V,\ terminated,\ 5\%$ to 95% duty cycle                                         |

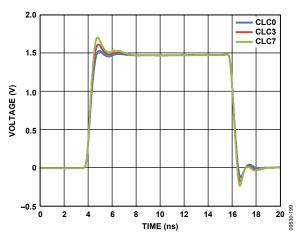

| Overshoot and Undershoot                                     |     | -116 |     | mV           | CB             | $VIH=2.0\ V,\ VIL=0.0\ V,\ terminated,\ driver\ CLC\ set\ to\ 0$                                       |

| Settling Time (VIH to VIL)                                   |     |      |     |              |                | Toggle DATx                                                                                            |

| To Within 3% of Final Value                                  |     | 1.7  |     | ns           | CB             | VIH = 2.0 V, VIL= 0.0 V, terminated                                                                    |

| To Within 1% of Final Value                                  |     | 45   |     | ns           | CB             | VIH = 2.0 V, VIL= 0.0 V, terminated                                                                    |

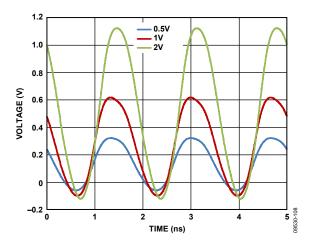

| Dynamic Performance,<br>VTerm (VIH or VIL to/from VIT)       |     |      |     |              |                | Toggle RCVx                                                                                            |

| Propagation Delay Time                                       |     | 1.39 |     | ns           | CB             | VIH = 2.0 V, VIT = 1.0 V, VIL = 0.0 V, terminated                                                      |

| Propagation Delay Tempco                                     |     | 2.3  |     | ps/°C        | CB             | VIH = 2.0 V, VIT = 1.0 V, VIL = 0.0 V, terminated                                                      |

| Transition Time, Active to VIT                               |     | 310  |     | ps           | CB             | 20% to 80%, VIH = 2.0 V, VIT = 1.0 V, VIL = 0.0 V, terminated                                          |

| Transition Time, VIT to Active                               |     | 329  |     | ps           | CB             | 20% to 80%, VIH = 2.0 V, VIT = 1.0 V, VIL = 0.0 V, terminated                                          |

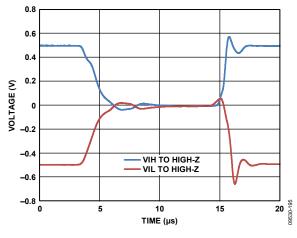

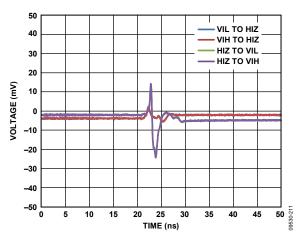

| Dynamic Performance,<br>Inhibit (VIH or VIL to/from Inhibit) |     |      |     |              |                | Toggle RCVx                                                                                            |

| Transition Time, Inhibit to Active                           |     | 357  |     | ps           | CB             | 20% to 80%, VIH = $+1.0$ V, VIL = $-1.0$ V, terminated                                                 |

| Transition Time, Active to Inhibit                           |     | 1.34 |     | ns           | CB             | 20% to 80%, VIH = +1.0 V, VIL = $-1.0$ V, terminated                                                   |

| Prop Delay, Inhibit to VIH                                   |     | 2.6  |     | ns           | Св             | VIH = +1.0 V, $VIL = -1.0 V$ , terminated; measured from RCV input crossing to DUTx pin output 50%     |

| Prop Delay, Inhibit to VIL                                   |     | 2.8  |     | ns           | CB             | VIH = +1.0 V, $VIL = -1.0 V$ , terminated                                                              |

| Prop Delay Matching,<br>Inhibit to VIL vs. Inhibit to VIH    |     | 52   |     | ps           | C <sub>B</sub> | VIH = +1.0 V, $VIL = -1.0 V$ , terminated                                                              |

| Prop Delay, VIH to Inhibit                                   |     | 2.29 |     | ns           | Св             | VIH = +1.0 V, $VIL = -1.0 V$ , terminated, measured from RCV:<br>input crossing to DUTx pin output 50% |

| Prop Delay, VIL to Inhibit                                   |     | 2.02 |     | ns           | CB             | VIH = +1.0 V, $VIL = -1.0 V$ , terminated                                                              |

| I/O Spike                                                    |     | 24   |     | mV pk-<br>pk | Св             | VIH = 0.0 V, $VIL = 0.0 V$ , terminated                                                                |

| Driver Pre-Emphasis (CLC)                                    | 1   |      |     |              |                |                                                                                                        |

| Pre-Emphasis Amplitude Rising                                | 1   | 35   |     | %            | CB             | VIH = 2.0 V, VIL = 0.0 V, terminated, DRV_CLC_x[15:13] = 7                                             |

|                                                              | 1   | 14   |     | %            | CB             | VIH = 2.0 V, VIL = 0.0 V, terminated, DRV_CLC_x[15:13] = 0                                             |

| Pre-Emphasis Amplitude Falling                               | 1   | 24   |     | %            | CB             | VIH = 2.0 V, VIL = 0.0 V, terminated, DRV_CLC_x[15:13] = 7                                             |

|                                                              |     | 16   |     | %            | CB             | VIH = 2.0 V, VIL = 0.0 V, terminated, DRV_CLC_x[15:13] = 0                                             |

| Parameter                  | Min | Тур | Max | Unit | Test<br>Level | Conditions                              |

|----------------------------|-----|-----|-----|------|---------------|-----------------------------------------|

| Pre-Emphasis Resolution    |     | 2   |     | %    | D             |                                         |

| Pre-Emphasis Time Constant |     | 0.8 |     | ns   | CB            | VIH = 2.0 V, $VIL = 0.0 V$ , terminated |

#### Table 3. Reflection Clamp (Clamp Accuracy Specifications Apply Only When VCH – VCL > 0.8 V)

| Parameter                   | Min  | Тур  | Max  | Unit   | Test<br>Level | Conditions                                                                                                                                                                                  |

|-----------------------------|------|------|------|--------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VCH/VCL PROGRAMMABLE RANGE  | -2.5 |      | +7.5 | V      | D             | DC specifications apply over full functional range unless noted.                                                                                                                            |

| VCH                         |      |      |      |        |               |                                                                                                                                                                                             |

| VCH Functional Range        | -1.2 |      | +7.0 | v      | D             |                                                                                                                                                                                             |

| VCH Offset Error            | -300 |      | +300 | mV     | Р             | Driver high-Z, sinking 1 mA, measured at DAC Code 0x4000, uncalibrated.                                                                                                                     |

| VCH Offset Tempco           |      | ±0.5 |      | mV/ºC  | CT            |                                                                                                                                                                                             |

| VCH Gain                    | 1.0  |      | 1.1  | V/V    | Ρ             | Driver high-Z, sinking 1 mA, gain derived from<br>measurements at DAC Code 0x4000 (0 V) and DAC Code<br>0xC000 (5 V), based on ideal DAC transfer function (see<br>Table 21).               |

| VCH Gain Tempco             |      | ±30  |      | ppm/°C | CT            |                                                                                                                                                                                             |

| VCH Resolution              |      | 153  |      | μV     | D             |                                                                                                                                                                                             |

| VCH DNL                     |      | ±1   |      | mV     | CT            | Driver high-Z, sinking 1 mA, after two point gain/offset<br>calibration; calibration points at DAC Code 0x4000 (0 V) and<br>DAC Code 0xC000 (5 V), measured over functional clamp<br>range. |

| VCH INL                     | -20  |      | +20  | mV     | Ρ             | Driver high-Z, sinking 1 mA, after two point gain/offset calibration; calibration points at 0x4000 (0 V) and 0xC000 (5 V), measured over functional clamp range.                            |

| VCL                         |      |      |      |        |               |                                                                                                                                                                                             |

| VCL Functional Range        | -2   |      | +6.2 | v      | D             |                                                                                                                                                                                             |

| VCL Offset Error            | -300 |      | +300 | mV     | Ρ             | Driver high-Z, sourcing 1 mA, measured at DAC Code 0x4000, uncalibrated.                                                                                                                    |

| VCL Offset Tempco           |      | ±0.5 |      | mV/°C  | CT            |                                                                                                                                                                                             |

| VCL Gain                    | 1.0  |      | 1.1  | V/V    | Ρ             | Drive high-Z, sourcing 1 mA, gain derived from<br>measurements at DAC Code 0x4000 (0 V) and DAC Code<br>0xC000 (5 V), based on ideal DAC transfer function (see<br>Table 21).               |

| VCL Gain Tempco             |      | ±30  |      | ppm/°C | C⊤            |                                                                                                                                                                                             |

| VCL Resolution              |      | 153  |      | μV     | D             |                                                                                                                                                                                             |

| VCL DNL                     |      | ±1   |      | mV     | CT            | Driver high-Z, sourcing 1 mA, after two point gain/offset calibration; calibration points at 0x4000 (0 V) and 0xC000 (+5 V), measured over functional clamp range.                          |

| VCL INL                     | -20  |      | +20  | mV     | Р             | Driver high-Z, sourcing 1 mA, after two point gain/offset calibration; calibration points at 0x4000 (0 V) and 0xC000 (+5 V), measured over functional clamp range.                          |

| DC Clamp Current Limit, VCH | -120 |      | -75  | mA     | Р             | Driver high-Z, VCH = 0 V, VCL = $-2.0$ V, VDUTx = $+5.0$ V.                                                                                                                                 |

| DC Clamp Current Limit, VCL | +75  |      | +120 | mA     | Р             | Driver high-Z, VCH = +6.0 V, VCL = +5.0 V, VDUTx = 0.0 V.                                                                                                                                   |

| DUTGND Voltage Accuracy     | -7   | ±2   | +7   | mV     | Ρ             | Over $\pm 0.1$ V range, measured at end points of VCH and VCL functional range.                                                                                                             |

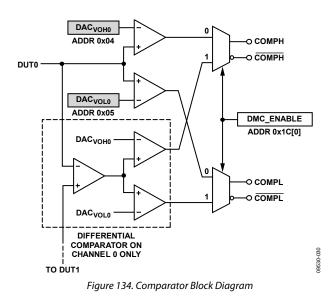

# Table 4. Normal Window Comparator (NWC) (Unless Otherwise Specified: VOH Tests at VOL = -1.5 V, VOL Tests at VOH = +6.5 V, Specifications Apply to Both Comparators)

| Parameter                                                       | Min           | Тур        | Max  | Unit   | Test<br>Level  | Conditions                                                                                                                                                                                                                                 |

|-----------------------------------------------------------------|---------------|------------|------|--------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DC SPECIFICATIONS                                               |               |            |      |        |                |                                                                                                                                                                                                                                            |

| Input Voltage Range                                             | -1.5          |            | +6.5 | v      | D              |                                                                                                                                                                                                                                            |

| Differential Voltage Range                                      | ±0.1          |            | ±8.0 | v      | D              |                                                                                                                                                                                                                                            |

| Comparator Input Offset Voltage                                 | -250          |            | +250 | mV     | Р              | Measured at DAC Code 0x4000 (0V), uncalibrated                                                                                                                                                                                             |

| Input Offset Voltage Tempco                                     |               | ±100       |      | μV/∘C  | C⊤             |                                                                                                                                                                                                                                            |

| Gain                                                            | 1.0           |            | 1.1  | v/v    | Ρ              | Gain derived from measurements at DAC Code<br>0x4000 (0 V) and DAC Code 0xC000 (5 V); based on<br>ideal DAC transfer function (see Table 21)                                                                                               |

| Gain Tempco                                                     |               | ±25        |      | ppm/°C | CT             |                                                                                                                                                                                                                                            |

| Threshold Resolution                                            |               | 153        |      | μV     | D              |                                                                                                                                                                                                                                            |

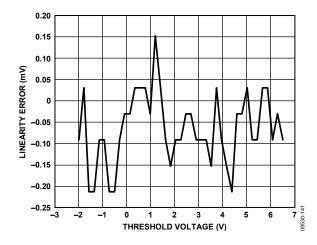

| Threshold DNL                                                   |               | ±1         |      | mV     | CT             | Measured over –1.5 V to +6.5 V functional range after two point gain/offset calibration; calibration points at 0x4000 (0 V) and 0xC000 (5 V)                                                                                               |

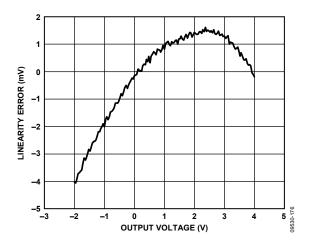

| Threshold INL                                                   | -7            |            | +7   | mV     | Р              | Measured over –1.5 V to +6.5 V functional range after two point gain/offset calibration; calibration points at 0x4000 (0 V) and 0xC000 (5 V)                                                                                               |

| DUTGND Voltage Accuracy                                         | -7            | ±2         | +7   | mV     | Р              | Over $\pm 0.1$ V range; measured at end points of VOH and VOL functional range                                                                                                                                                             |

| Uncertainty Band                                                |               | 5          |      | mV     | Св             | VDUTx = 0 V, sweep comparator threshold to determine the uncertainty band                                                                                                                                                                  |

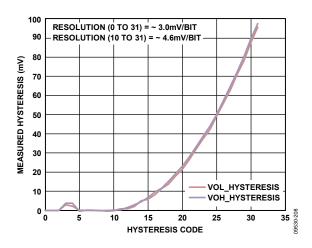

| Maximum Programmable Hysteresis                                 |               | 96         |      | mV     | CB             |                                                                                                                                                                                                                                            |

| Hysteresis Resolution                                           |               | 5          |      | mV     | D              | Calculated over hystersis control Code 10 to Code 3                                                                                                                                                                                        |

| DC PSRR                                                         |               | ±5         |      | mV/V   | CT             | Measured at calibration points                                                                                                                                                                                                             |

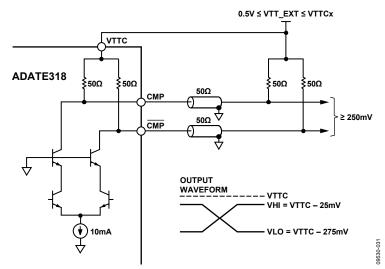

| Digital Output Characteristics                                  |               |            |      |        |                |                                                                                                                                                                                                                                            |

| Internal Pull-Up Resistance to<br>Comparator, VTTC              | 46            | 50         | 54   | Ω      | Р              | Pull 1 mA and 10 mA from Logic 1 leg and measure $\Delta V$ to calculate resistance; measured $\Delta V/9$ mA; done for both comparator logic states                                                                                       |

| Comparator Termination Voltage,<br>VTTC                         | 0.5           | 1.2        | 3.3  | V      | D              |                                                                                                                                                                                                                                            |

| Common Mode Voltage                                             |               | VTTC – 0.3 |      | V      | C⊤             | Measured with 100 $\boldsymbol{\Omega}$ differential termination                                                                                                                                                                           |

|                                                                 | VTTC –<br>0.5 |            | VTTC | V      | Р              | Measured with no external termination                                                                                                                                                                                                      |

| Differential Voltage                                            |               | 250        |      | mV     | C⊤             | Measured with 100 $\boldsymbol{\Omega}$ differential termination                                                                                                                                                                           |

|                                                                 | 450           | 500        | 550  | mV     | Р              | Measured with no external termination                                                                                                                                                                                                      |

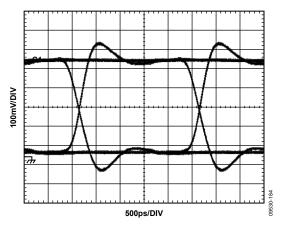

| Rise/Fall Times, 20% to 80%                                     |               | 166        |      | ps     | CB             | Measured with 50 $\Omega$ to external termination voltage (VTTC)                                                                                                                                                                           |

| AC SPECIFICATIONS                                               |               |            |      |        |                | All ac specifications performed after dc level<br>calibration, input transition time of ~200 ps, 20% to<br>80%, measured with 50 $\Omega$ to external termination<br>voltage (VTTC); peaking set to CLC = 2, unless<br>otherwise specified |

| Propagation Delay, Input to Output                              |               | 0.93       |      | ns     | C <sub>B</sub> | VDUTx: 0 V to 1.0 V swing, driver term mode,<br>VIT = 0.0 V, comparator threshold = 0.5 V                                                                                                                                                  |

| Propagation Delay Tempco                                        |               | 1.6        |      | ps/ºC  | CB             | VDUTx: 0 V to 1.0 V swing, driver term mode,<br>VIT = 0.0 V, comparator threshold = 0.5 V                                                                                                                                                  |

| Propagation Delay Matching<br>High Transition to Low Transition |               | 7          |      | ps     | CB             | VDUTx: 0 V to 1.0 V swing, driver term mode,<br>VIT = 0.0 V, comparator threshold = 0.5 V                                                                                                                                                  |

| Propagation Delay Matching<br>High to Low Comparator            |               | 7          |      | ps     | C <sub>B</sub> | VDUTx: 0 V to 1.0 V swing, driver term mode,<br>VIT = 0.0 V, comparator threshold = 0.5 V                                                                                                                                                  |

| Parameter                                      | Min | Тур     | Max | Unit         | Test<br>Level  | Conditions                                                                                                                                                                                                         |

|------------------------------------------------|-----|---------|-----|--------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Propagation Delay Dispersion                   |     |         |     |              |                |                                                                                                                                                                                                                    |

| Slew Rate<br>400 ps vs. 1 ns (20% to 80%)      |     | 19      |     | ps           | C <sub>B</sub> | VDUTx: 0 V to 0.5 V swing, driver term mode,<br>VIT = 0.0 V, comparator threshold = 0.25 V                                                                                                                         |

| Overdrive<br>250 mV vs. 1.0 V                  |     | 40      |     | ps           | CB             | For 250 mV, VDUTx: 0 V to 0.5 V swing; for 1.0 V,<br>VDUTx: 0 V to 1.25 V swing, driver term mode,<br>VIT = 0.0 V, comparator threshold = 0.25 V                                                                   |

| 1 V Pulse Width<br>0.7 ns, 1 ns, 5 ns, 10 ns   |     | +2/- 17 |     | ps           | C <sub>B</sub> | VDUTx: 0 V to 1.0 V swing at~32.0 MHz; driver term mode, VIT = 0.0 V, comparator threshold = 0.5 V                                                                                                                 |

| 0.5 V Pulse Width<br>0.6 ns, 1 ns, 5 ns, 10 ns |     | +3/- 24 |     | ps           | CB             | VDUTx: 0 V to 0.5 V swing at~32.0 MHz, driver term mode, VIT = 0.0 V; comparator threshold = 0.25 V                                                                                                                |

| Duty Cycle<br>5% to 95%                        |     | 21      |     | ps           | CB             | VDUTx: 0 V to 1.0 V swing at~32.0 MHz; driver term mode, VIT =0.0 V, comparator threshold = 0.5 V                                                                                                                  |

| Minimum Detectable Pulse Width                 |     | 0.5     |     | ns           | C <sub>B</sub> | VDUTx: 0 V to 1.0 V swing at 32.0 MHz, driver term<br>mode, VIT = 0.0 V; greater than 50% output<br>differential amplitude                                                                                         |

| Input Equivalent Bandwidth,<br>Terminated      |     | 1520    |     | MHz          | CB             | $ \begin{array}{l} VDUTx: 0 \ V \ to \ 1.0 \ V \ swing; \ driver \ term \ mode, \\ VIT = 0.0 \ V, \ CLC = 2; \ as \ measured \ by \ shmoo \ plot; \\ f_{EQUV} = 0.22/\sqrt{(t_{MEAS}^2 - t_{DUT}^2)} \end{array} $ |

| ERT High-Z Mode, 3 V, 20% to 80%               |     | 721     |     | ps           | Св             | VDUTx: 0 V to 3.0 V swing, driver high-Z as measured by shmoo plot; $f_{EQUIV} = 0.22/\sqrt{(t_{MEAS}^2 - t_{DUT}^2)}$                                                                                             |

| Comparator Pre-Emphasis (CLC)                  |     |         |     |              |                |                                                                                                                                                                                                                    |

| CLC Amplitude Range                            |     | 16      |     | %            | CB             | VDUTx: 0 V to 1.0 V swing, driver term mode,<br>VIT = 0.0 V, comparator pre-emphasis set to<br>maximum                                                                                                             |

| CLC Resolution                                 |     | 2.3     |     | % per<br>bit | C <sub>B</sub> | 3-bit amplitude control                                                                                                                                                                                            |

| Pre-Emphasis Time Constant                     |     | 4.3     |     | ns           | C <sub>B</sub> | VDUTx: 0 V to 1.0 V swing, driver term mode,<br>VIT = 0.0 V, comparator pre-emphasis set to<br>maximum                                                                                                             |

# Table 5. Differential Mode Comparator (DMC) (Unless Otherwise Specified: VOH Tests at VOL = -1.1 V, VOL Tests at VOH = +1.1 V)

| Parameter                     | Min   | Тур  | Max  | Unit   | Test<br>Level  | Conditions                                                                                                                                                                         |

|-------------------------------|-------|------|------|--------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DC SPECIFICATIONS             |       |      |      |        |                |                                                                                                                                                                                    |

| Input Voltage Range           | -1.5  |      | +6.5 | V      | D              |                                                                                                                                                                                    |

| Functional Differential Range | ±0.05 |      | ±1.1 | v      | D              |                                                                                                                                                                                    |

| Maximum Differential Input    |       |      | ±8   | v      | D              |                                                                                                                                                                                    |

| Input Offset Voltage          | -250  |      | +250 | mV     | Р              | Offset extrapolated from measurements at DAC Code 0x2666 (–1 V) and DAC Code 0x599A (+1 V), with $V_{CM} = 0$ V                                                                    |

| Offset Voltage Tempco         |       | ±150 |      | μV/ºC  | CT             |                                                                                                                                                                                    |

| Gain                          | 1.0   |      | 1.1  | V/V    | Ρ              | Gain derived from measurements at DAC Code 0x2666<br>(–1 V) and DAC Code 0x599A (+1 V), based on ideal DAC<br>transfer function (see Table 21)                                     |

| Gain Tempco                   |       | ±25  |      | ppm/°C | C⊤             |                                                                                                                                                                                    |

| VOH, VOL Resolution           |       | 153  |      | μV     | D              |                                                                                                                                                                                    |

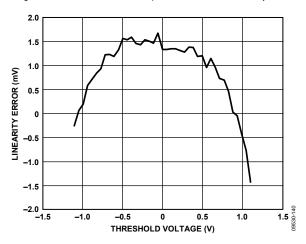

| VOH, VOL DNL                  |       | ±1   |      | mV     | CT             | After two point gain/offset calibration, $V_{CM} = 0.0 V$ , calibration points at 0x2666 ( $-1 V$ ) and 0x599A ( $+1 V$ )                                                          |

| VOH, VOL INL                  | -7    |      | +7   | mV     | Ρ              | After two point gain/offset calibration, measured over VOH/VOL range of $-1.1$ V to $+1.1$ V, V <sub>CM</sub> = 0.0 V; calibration points at 0x2666 ( $-1$ V) and 0x599A ( $+1$ V) |

| Uncertainty Band              |       | 7    |      | mV     | C <sub>B</sub> | VDUTx = 0 V; sweep comparator threshold to determine the uncertainty band                                                                                                          |

| Parameter                                                           | Min | Тур        | Max | Unit      | Test<br>Level  | Conditions                                                                                                                                                                                                                                       |

|---------------------------------------------------------------------|-----|------------|-----|-----------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

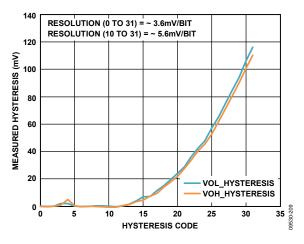

| Maximum Programmable<br>Hysteresis                                  |     | 117        |     | mV        | CB             |                                                                                                                                                                                                                                                  |

| Hysteresis Resolution                                               |     | 5.6        |     | mV        | D              | Calculated over hystersis control Code 10 to Code 31                                                                                                                                                                                             |

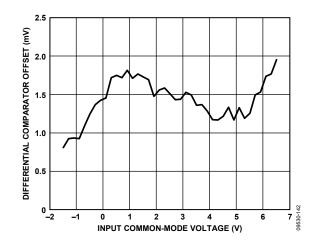

| CMRR                                                                | -1  |            | +1  | mV/V      | Р              | Offset measured at $V_{\text{CM}} = -1.5$ V and $+6.5$ V with $V_{\text{DM}} = 0.0$ V offset error change                                                                                                                                        |

| DC PSRR                                                             |     | ±5         |     | mV/V      | CT             | Measured at calibration points                                                                                                                                                                                                                   |

| AC SPECIFICATIONS                                                   |     |            |     |           |                | All ac specifications performed after dc level calibration,<br>unless noted; input transition time ~200 ps, 20% to 80%,<br>measured with 50 $\Omega$ to external termination voltage (VTTC<br>peaking set to CLC = 2, unless otherwise specified |

| Propagation Delay,<br>Input to Output                               |     | 0.83       |     | ns        | Св             | VDUT0 = 0 V, VDUT1: $-0.5$ V to $+0.5$ V swing, driver term<br>mode, VIT = 0.0 V, comparator threshold = 0.0 V, repeat for<br>other channel                                                                                                      |

| Propagation Delay Tempco                                            |     | 2.6        |     | ps/ºC     | CB             | VDUT0 = 0 V, VDUT1: -0.5 V to +0.5 V swing, driver term<br>mode, VIT = 0.0 V, comparator threshold = 0.0 V, repeat for<br>other channel                                                                                                          |

| Propagation Delay Matching,<br>High Transition to Low<br>Transition |     | 15         |     | ps        | C <sub>B</sub> | VDUT0 = 0 V, VDUT1: -0.5 V to +0.5 V swing, driver term<br>mode, VIT = 0.0 V, comparator threshold = 0.0 V, repeat for<br>other channel                                                                                                          |

| Propagation Delay Matching,<br>High to Low Comparator               |     | 17         |     | ps        | C <sub>B</sub> | VDUT0 = 0 V, VDUT1: -0.5 V to +0.5 V swing, driver term<br>mode, VIT = 0.0 V, comparator threshold = 0.0 V, repeat for<br>other channel                                                                                                          |

| Propagation Delay Change<br>(Dispersion) With Respect To            |     |            |     |           |                |                                                                                                                                                                                                                                                  |

| Slew Rate:<br>400 ps and 1 ns<br>(20% to 80%)                       |     | 31         |     | ps        | CB             | VDUT0 = 0.0 V; VDUT1: -0.5 V to +0.5 V swing; driver term<br>mode, VIT = 0.0 V; comparator threshold = 0.0 V, repeat for<br>other channel                                                                                                        |

| Overdrive:<br>250 mV and 750 mV                                     |     | 32         |     | ps        | C <sub>B</sub> | VDUT0 = 0.0 V; for 250 mV: VDUT1: 0 V to 0.5 V swing; for<br>750 mV: VDUT1: 0 V to 1.0 V swing; driver term mode,<br>VIT = 0.0 V; comparator threshold = -0.25 V; repeat for<br>other channel with comparator threshold = +0.25 V                |

| 1 V Pulse Width:<br>0.7 ns, 1 ns, 5 ns, 10 ns                       |     | +1/-<br>21 |     | ps        | CB             | VDUT0 = 0.0 V; VDUT1: $-0.5$ V to $+0.5$ V swing at 32 MHz;<br>driver term mode, VIT = 0.0 V; comparator threshold = 0.0 V<br>repeat for other channel                                                                                           |

| 0.5 V Pulse Width:<br>0.6 ns, 1 ns, 5 ns, 10 ns                     |     | +1/-<br>31 |     | ps        | C <sub>B</sub> | VDUT0 = 0.0 V; VDUT1: $-0.25$ V to $+0.25$ V swing at 32 MHz<br>driver term mode, VIT = 0.0 V; comparator threshold = 0.0 V<br>repeat for other channel                                                                                          |

| Duty Cycle:<br>5% to 95%                                            |     | 18         |     | ps        | Св             | VDUT0 = 0.0 V; VDUT1: $-0.5$ V to $+0.5$ V swing at 32 MHz;<br>driver term mode, VIT = 0.0 V; comparator threshold = 0.0 V<br>repeat for other channel                                                                                           |

| Minimum Detectable<br>Pulse Width                                   |     | 0.5        |     | ns        | CB             | VDUT0 = 0.0 V; VDUT1: -0.5 V to +0.5 V swing at 32 MHz;<br>driver term mode, VIT = 0.0 V; comparator threshold = 0.0 V<br>greater than 50% output differential amplitude; repeat for<br>other channel                                            |

| Input Equivalent Bandwidth,<br>Terminated                           |     | 1038       |     | MHz       | Св             | VDUT0 = 0.0 V; VDUT1: -0.5 V to +0.5 V swing; driver term<br>mode, VIT = 0.0 V; comparator threshold = 0.0 V, CLC = 2 as<br>measured by shmoo; repeat for other channel                                                                          |

| Comparator Pre-Emphasis (CLC)                                       |     |            |     |           |                |                                                                                                                                                                                                                                                  |

| CLC Amplitude Range                                                 |     | 11         |     | %         | C <sub>B</sub> | VDUT0 = 0.0 V; VDUT1: -0.8 V to +0.8 V swing, driver term<br>mode, VIT = 0.0 V; comparator threshold = 0.0 V;<br>comparator CLC set to maximum; repeat for other channel                                                                         |

| CLC Resolution                                                      |     | 1.6        |     | % per bit | CB             | 3-bit amplitude control                                                                                                                                                                                                                          |

| Pre-Emphasis Time Constant                                          |     | 4.8        |     | ns        | C <sub>B</sub> | VDUT0 = 0.0 V; VDUT1: -0.8 V to +0.8 V swing, driver term<br>mode, VIT = 0.0 V; comparator threshold = 0.0 V;<br>comparator CLC set to maximum; repeat for other channel                                                                         |

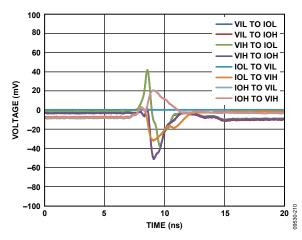

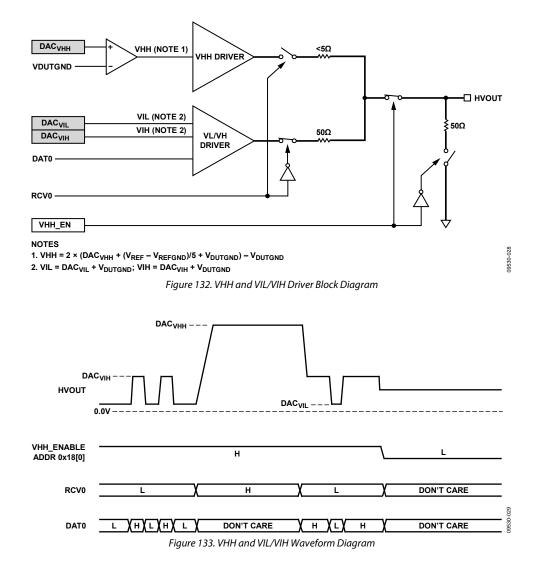

#### Table 6. Active Load

| Parameter                      | Min  | Тур  | Max  | Unit   | Test<br>Level | Conditions                                                                                                                                                                                               |

|--------------------------------|------|------|------|--------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DC SPECIFICATIONS              |      |      |      |        |               | Load active on, RCVx active, unless otherwise noted                                                                                                                                                      |

| Input Characteristics          |      |      |      |        |               |                                                                                                                                                                                                          |

| VCOM Voltage Range             | -1.5 |      | +6.5 | v      | D             | $ $ IOL and IOH $  \le 1 \text{ mA}$                                                                                                                                                                     |

|                                | -1.0 |      | +5.5 | v      | D             | IOL and IOH   ≤ 25 mA                                                                                                                                                                                    |

| VCOM Offset                    | -200 |      | +200 | mV     | Р             | Measured at DAC Code 0x4000, uncalibrated                                                                                                                                                                |

| VCOM Offset Tempco             |      | ±25  |      | μV/°C  | CT            |                                                                                                                                                                                                          |

| VCOM Gain                      | 1.0  |      | 1.1  | V/V    | Ρ             | Gain derived from measurements at DAC Code 0x4000 (0 V) and DAC Code 0xC000 (+5 V), based on ideal DAC transfer function (see Table 21)                                                                  |

| VCOM Gain Tempco               |      | ±25  |      | ppm/°C | CT            |                                                                                                                                                                                                          |

| VCOM Resolution                |      | 153  |      | μV     | D             |                                                                                                                                                                                                          |

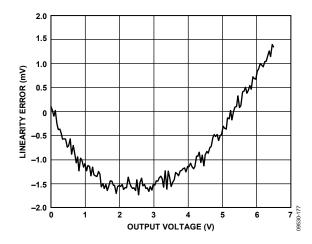

| VCOM DNL                       |      | ±1   |      | mV     | CT            | IOH = IOL = 12.5 mA; after two point gain/offset calibration;<br>measured over VCOM range of $-1.5$ V to $+6.5$ V; calibration points<br>at 0x4000 (0 V) and 0xC000 (+5 V)                               |

| VCOM INL                       | -7   |      | +7   | mV     | Р             | IOH = IOL = 12.5 mA; after two point gain/offset calibration;<br>measured at end points of VCOM functional range                                                                                         |

| DUTGND Voltage<br>Accuracy     | -7   | ±2   | +7   | mV     | Р             | Over ±0.1 V range                                                                                                                                                                                        |

| Output Characteristics         |      |      |      |        |               |                                                                                                                                                                                                          |

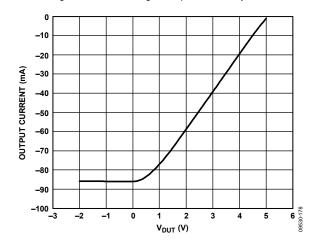

| Maximum Source<br>Current      | 25   |      |      | mA     | D             | –1.5 V to +5.5 V DUT range                                                                                                                                                                               |

| IOL Offset                     | -600 |      | +600 | μΑ     | Ρ             | IOH = $-2.5$ mA, VCOM = $1.5$ V, VDUTx = $0.0$ V; offset extrapolated from measurements at DAC Code $0x451F$ (1 mA) and DAC Code $0xA666$ (20 mA)                                                        |

| IOL Offset Tempco              |      | ±1   |      | μA/°C  | CT            |                                                                                                                                                                                                          |

| IOL Gain Error                 | 0    |      | 25   | %      | Ρ             | IOH = $-2.5$ mA, VCOM = $1.5$ V, VDUTx = $0.0$ V; gain derived from measurements at DAC Code 0x451F (1 mA) and DAC Code 0xA666 (20 mA); based on ideal DAC transfer function (see Table 21 and Table 22) |

| IOL Gain Tempco                |      | ±25  |      | ppm/°C | CT            |                                                                                                                                                                                                          |

| IOL Resolution                 |      | 763  |      | nA     | D             |                                                                                                                                                                                                          |

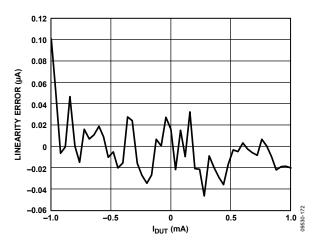

| IOL DNL                        |      | ±4   |      | μΑ     | C⊤            | IOH = -2.5  mA, VCOM = 1.5 V, VDUTx = 0.0 V; after two point gain/offset calibration; measured over IOL range, 0 mA to 25 mA; calibrated at Code 0x451F (1 mA) and Code 0xA666 (20 mA)                   |

| IOL INL                        | -100 | ±20  | +100 | μΑ     | Р             | IOH = $-2.5$ mA, VCOM = $1.5$ V, VDUTx = $0.0$ V; after two point gain/offset calibration                                                                                                                |

| IOL 90% Commutation<br>Voltage |      | 0.25 | 0.4  | V      | Ρ             | IOH = IOL = 25 mA, VCOM = 2.0 V; measure IOL reference at VDUTx = $-1.0$ V; measure IOL current at VDUTx = 1.6 V; check >90% of reference current                                                        |

| IOL 90% Commutation<br>Voltage |      | 0.1  |      | V      | CT            | IOH = IOL = 1 mA, VCOM = 2.0 V; measure IOL reference at VDUTx = $-1.0$ V; measure IOL current at VDUTx = 1.9 V; check >90% of reference current                                                         |

| Maximum Sink Current           | 25   |      |      | mA     | D             | –1.0 V to +6.5 V output range                                                                                                                                                                            |

| IOH Offset                     | -600 |      | +600 | μΑ     | Р             | IOL = $-2.5$ mA, VCOM = $1.5$ V, VDUTx = $3.0$ V; offset extrapolated from measurements at DAC Code $0x451F$ (1 mA) and DAC Code $0xA666$ (20 mA)                                                        |

| IOH Offset Tempco              |      | ±1   |      | µA/°C  | CT            |                                                                                                                                                                                                          |

| IOH Gain Error                 | 0    |      | 25   | %      | Ρ             | IOL = -2.5  mA, VCOM = 1.5 V, VDUTx = 3.0 V; gain derived from measurements at DAC Code 0x451F (1 mA) and DAC Code 0xA666 (20 mA); based on ideal DAC transfer function (see Table 21 and Table 22)      |

| Parameter                                                            | Min  | Тур  | Max  | Unit         | Test<br>Level  | Conditions                                                                                                                                                                                                                                       |

|----------------------------------------------------------------------|------|------|------|--------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IOH Gain Tempco                                                      |      | ±25  |      | ppm/°C       | CT             |                                                                                                                                                                                                                                                  |

| IOH Resolution                                                       |      | 763  |      | nA           | D              |                                                                                                                                                                                                                                                  |

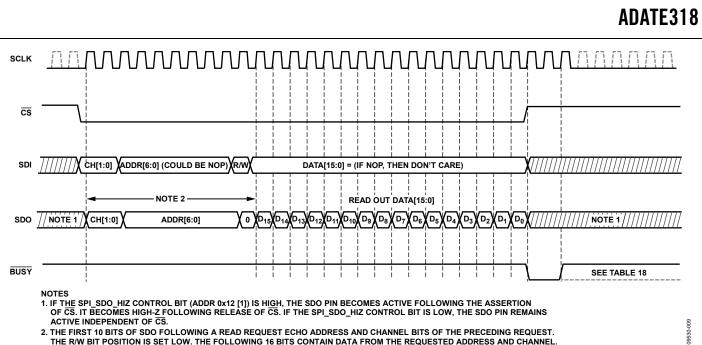

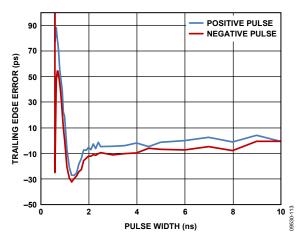

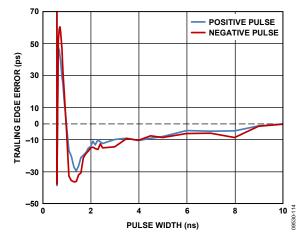

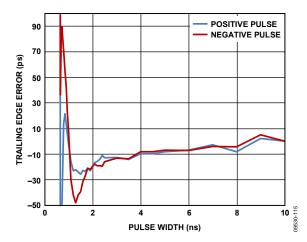

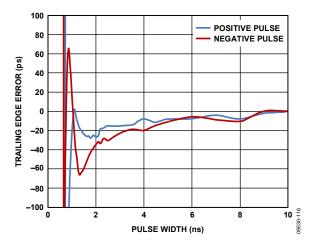

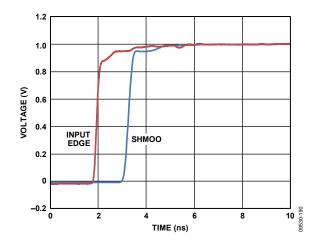

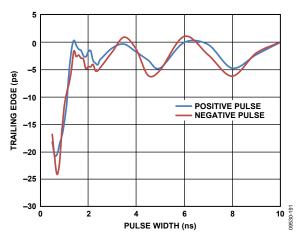

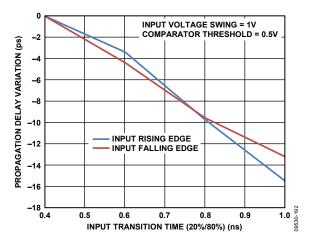

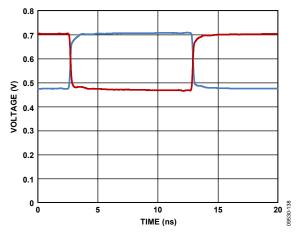

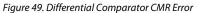

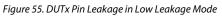

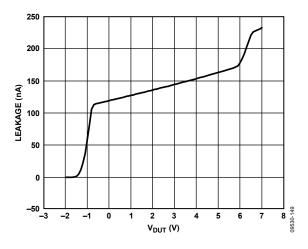

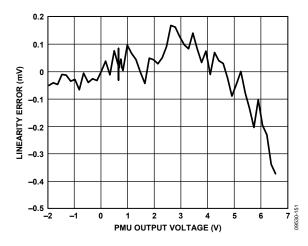

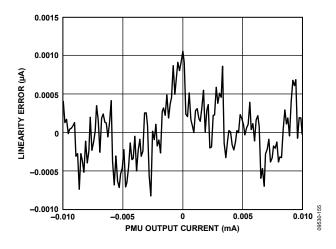

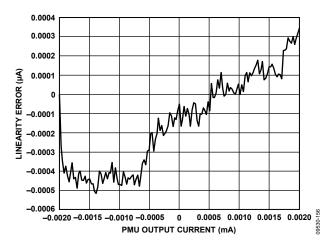

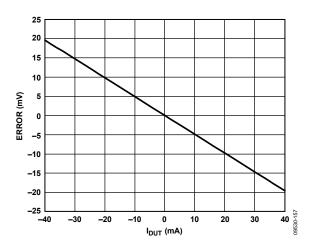

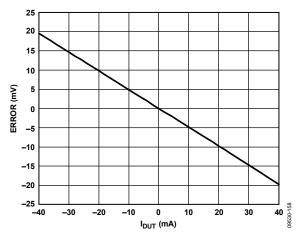

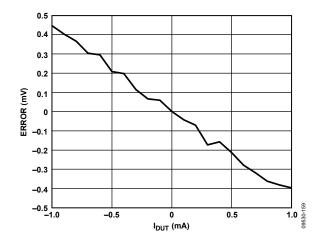

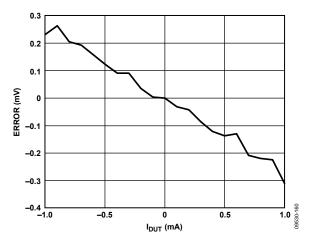

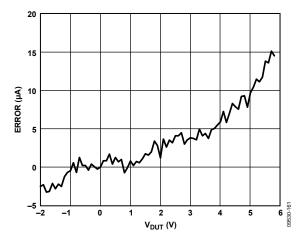

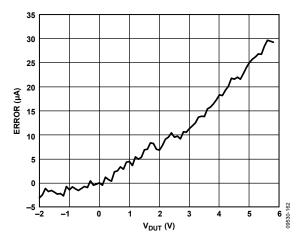

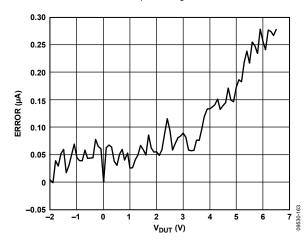

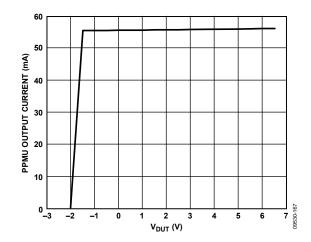

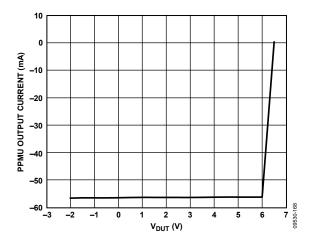

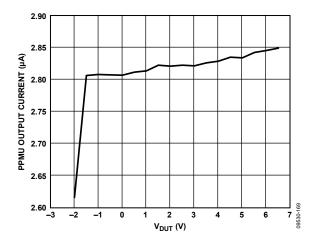

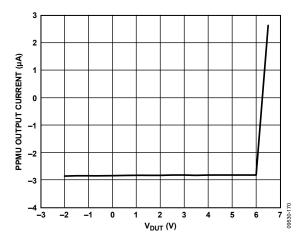

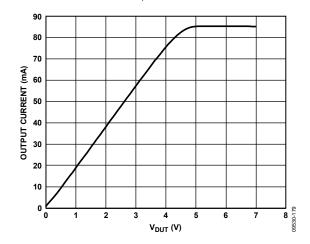

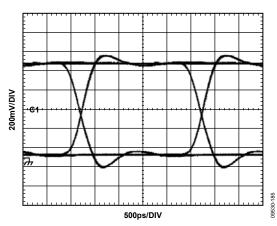

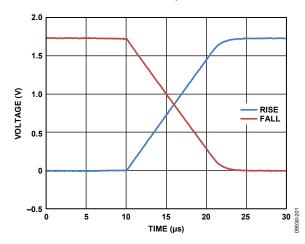

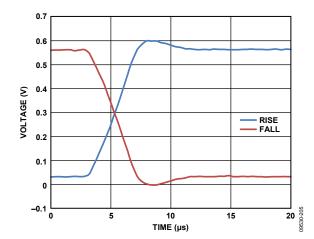

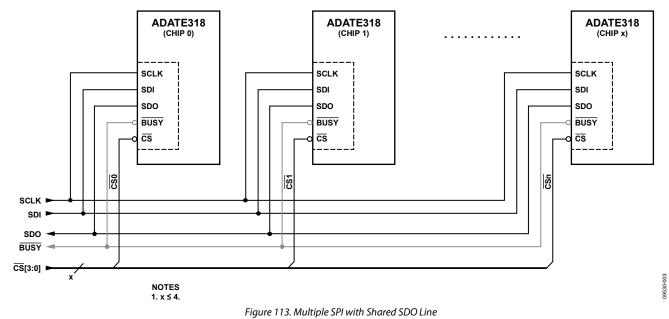

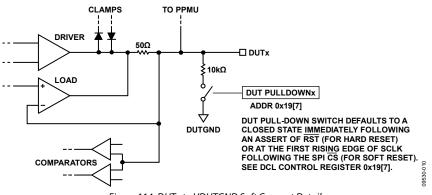

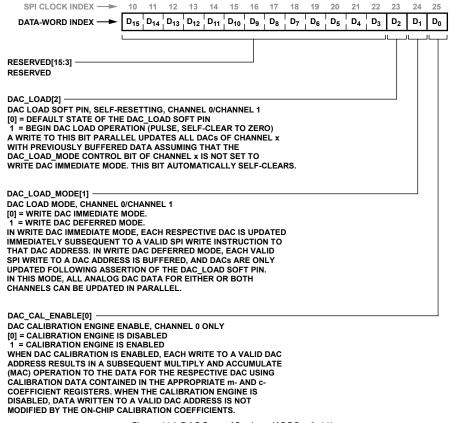

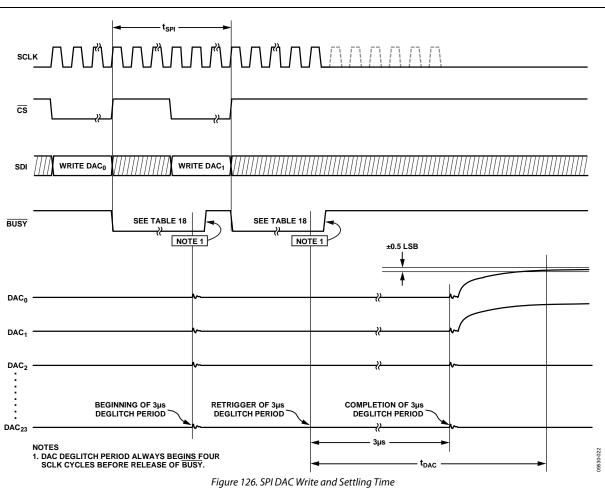

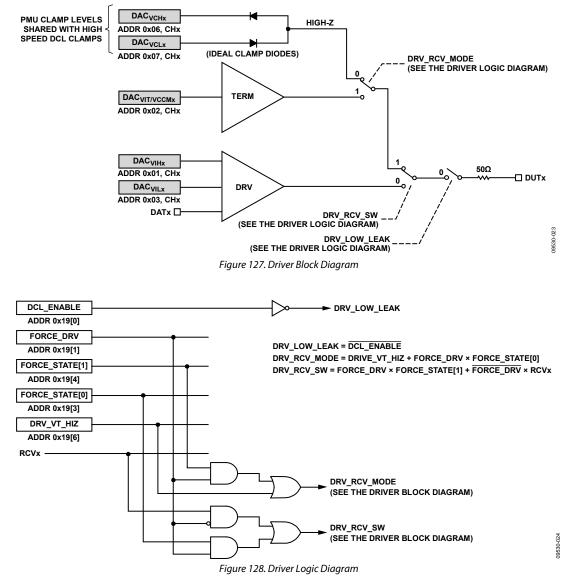

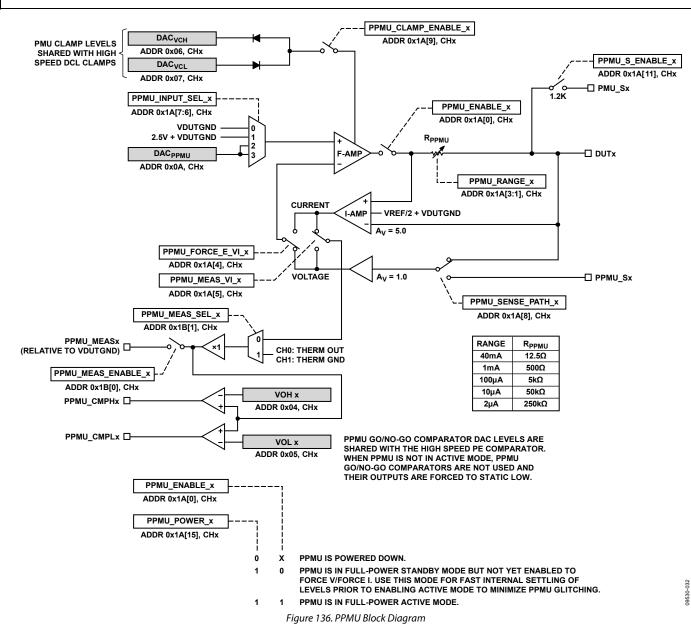

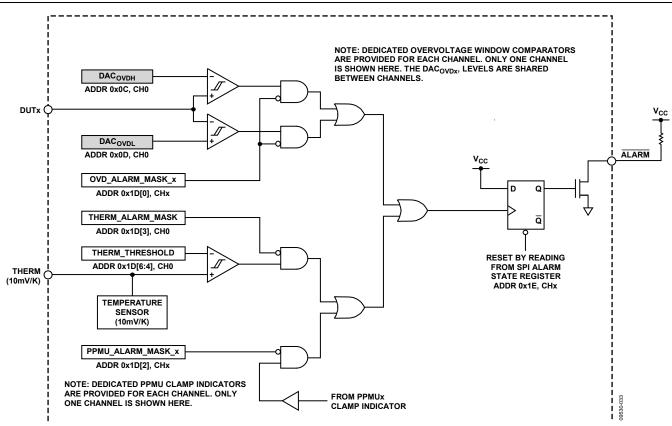

| IOH DNL                                                              |      | ±4   |      | μΑ           | Ст             | IOL = -2.5  mA, VCOM = 1.5 V, VDUTx = 3.0 V; after two point gain/offset calibration; measured over IOH range, 0 mA to 25 mA; calibrated at Code 0x451F (1 mA) and Code 0xA666 (20 mA)                                                           |